Paggamitoptoelektronikoteknolohiya ng co-packaging upang malutas ang napakalaking pagpapadala ng data

Dahil sa pag-unlad ng computing power sa mas mataas na antas, mabilis na lumalawak ang dami ng data, lalo na ang mga bagong data center business traffic tulad ng malalaking modelo ng AI at machine learning na nagtataguyod ng paglago ng data mula sa dulo hanggang dulo at sa mga gumagamit. Kailangang mabilis na mailipat ang napakalaking data sa lahat ng anggulo, at ang bilis ng pagpapadala ng data ay umunlad din mula 100GbE hanggang 400GbE, o kahit 800GbE, upang matugunan ang tumataas na pangangailangan sa computing power at data interaction. Habang tumataas ang mga line rate, ang board-level complexity ng mga kaugnay na hardware ay lubos na tumaas, at ang tradisyonal na I/O ay hindi nakayanan ang iba't ibang pangangailangan ng pagpapadala ng mga high-speed signal mula sa mga ASic patungo sa front panel. Sa kontekstong ito, hinahanap-hanap ang CPO optoelectronic co-packaging.

Pagtaas ng demand sa pagproseso ng datos, CPOoptoelektronikoatensyon na co-seal

Sa sistema ng komunikasyong optikal, ang optical module at ang AISC (Network switching chip) ay nakabalot nang hiwalay, at angmodyul na optikalay nakasaksak sa harap na panel ng switch sa isang pluggable mode. Hindi na bago ang pluggable mode, at maraming tradisyonal na koneksyon sa I/O ang magkakasamang nakakonekta sa pluggable mode. Bagama't ang pluggable pa rin ang unang pagpipilian sa teknikal na ruta, ang pluggable mode ay naglantad ng ilang problema sa mataas na data rates, at ang haba ng koneksyon sa pagitan ng optical device at ng circuit board, pagkawala ng signal transmission, pagkonsumo ng kuryente, at kalidad ay malilimitahan dahil ang bilis ng pagproseso ng data ay kailangang dagdagan pa.

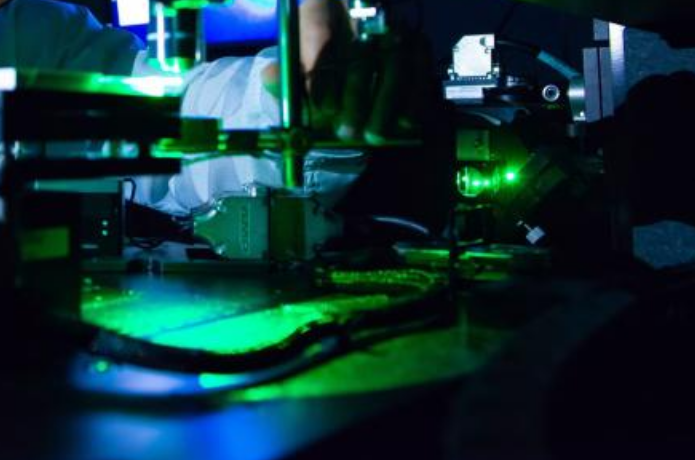

Upang malutas ang mga limitasyon ng tradisyonal na koneksyon, ang CPO optoelectronic co-packaging ay nagsimulang makatanggap ng atensyon. Sa Co-packaged optics, ang mga optical module at AISC (Network switching chips) ay pinagsama-sama at pinagdudugtong sa pamamagitan ng mga short-distance electrical connection, kaya nakakamit ang compact optoelectronic integration. Ang mga bentahe ng laki at bigat na dulot ng CPO photoelectric co-packaging ay halata, at ang pagpapaliit at pagpapaliit ng mga high-speed optical module ay natatanto. Ang optical module at AISC (Network switching chip) ay mas sentralisado sa board, at ang haba ng fiber ay maaaring mabawasan nang malaki, na nangangahulugang ang pagkawala sa panahon ng transmisyon ay maaaring mabawasan.

Ayon sa datos ng pagsubok ng Ayar Labs, ang CPO opto-co-packaging ay maaaring direktang makabawas sa pagkonsumo ng kuryente ng kalahati kumpara sa mga pluggable optical module. Ayon sa kalkulasyon ng Broadcom, sa 400G pluggable optical module, ang CPO scheme ay maaaring makatipid ng humigit-kumulang 50% sa pagkonsumo ng kuryente, at kumpara sa 1600G pluggable optical module, ang CPO scheme ay maaaring makatipid ng mas maraming pagkonsumo ng kuryente. Ang mas sentralisadong layout ay nagpapalaki rin ng densidad ng interconnection, nagpapabuti sa pagkaantala at pagbaluktot ng electrical signal, at ang paghihigpit sa bilis ng transmission ay hindi na katulad ng tradisyonal na pluggable mode.

Isa pang punto ay ang gastos. Ang mga sistema ng artificial intelligence, server, at switch ngayon ay nangangailangan ng napakataas na densidad at bilis. Mabilis na tumataas ang kasalukuyang demand. Kung wala ang CPO co-packaging, kailangan ang maraming high-end connectors para ikonekta ang optical module, na isang malaking gastos. Malaking bahagi rin ng pagbabawas ng BOM ang CPO co-packaging para mabawasan ang bilang ng mga connector. Ang CPO photoelectric co-packaging ang tanging paraan para makamit ang high speed, high bandwidth, at low power network. Ang teknolohiyang ito ng pagsasama-sama ng packaging ng silicon photoelectric components at electronic components ay ginagawang mas malapit ang optical module sa network switch chip hangga't maaari upang mabawasan ang channel loss at impedance discontinuity, lubos na mapabuti ang interconnection density, at magbigay ng teknikal na suporta para sa mas mataas na rate ng koneksyon ng data sa hinaharap.

Oras ng pag-post: Abr-01-2024